智能变电站的稳定运行靠什么来保障?

智能变电站的二次系统通常包含电子式互感器、合并单元、交换机、保护测控等设备。这些装置必须基于统一的时间基准运行,这对智能变电站的时钟同步系统提出严格的要求。智能变电站微秒级的对时系统究竟是如何实现的呢?

时间是基本物理量,那么时间也就会有精度的问题,不同时间源有着不同的精度。如AppleWatch与iPhone配合使用,同UTC时间误差不超过50ms。50ms误差对于人类的感知可以忽略,可是如果用在智能变电站中就显得不尽人意了。

智能变电站的二次系统通常包含电子式互感器、合并单元、交换机、保护测控等设备。这些装置必须基于统一的时间基准运行,方能满足事件顺序记录(SOE)、故障录波、实时数据采集时间一致性的要求,确保线路故障测距、相量和攻角动态监测、机组和电网参数校验的准确性。这些要求对智能变电站的时钟同步系统提出严格的要求。

IEC61850标准将变电站分为站空层、间隔层和过程层,对时间同步精度的要求,各层设备是不同的。间隔层设备需要到达ms精度;而过程层设备,由于主要传输采样值、跳闸信息,需要达到μs的同步精度。智能变电站的测试设备DT6000系列(DT6000、DT6000E和DT6000S)的对时精度可达μs的同步精度,完全满足变电站各层的设备的对时精度。

DT6000系列的对时系统

图1.1DT6000系列的对时

DT6000系列的对时支持IRIG-B、PPS和IEEE1588三种对时,如图1.1所示。三种协议全部采用FPGA硬解码,解码之后转换为UTC时标,提供时间给SMV、GOOSE等其他协议,如SMV和GOOSE的接收的时标为硬时标,由FPGA进行打时标,将时间信息插入报文中,实时保存报文信息和时间。在对时的同时,FPGA还进行了校时,即将本地晶振引起的误差(μs级)进行校正,动态调整均匀调节误差值。

一、对时

1.PPS对时

检测PPS正常与否,有两个重要的判别依据:

(1)相邻脉冲上升沿的时间间隔为1s。当相邻脉冲上升沿的间隔时间与理想间隔时间(1s)相差大于10μs时,则判定输入异常。

(2)脉冲宽度大于10μs,间隔大于500ms。当测量到的脉冲宽度小于10μs,或者测量到的脉冲间隔小于500ms时,则认为输入异常。

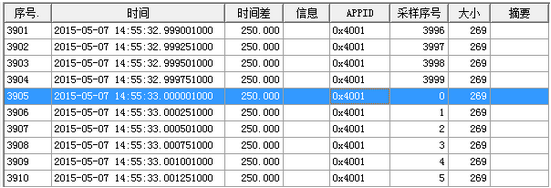

DT6000系列根据上述两个判别依据并将输入的信号进行了过滤,去除毛刺信号。如图1.2所示为DT6000E经过PPS对时之后,SMV采样计数器在整秒清零。

图1.2整秒SMV采样计数器清零

2.IRIG-B对时

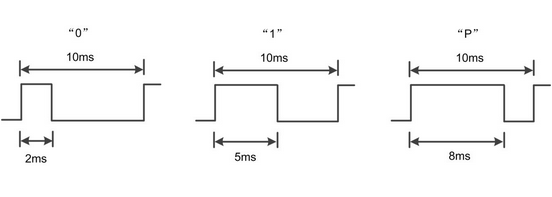

IRIG-B码的帧周期是1s,包含100个码元,每个码元周期为10ms,即IRIG-B码的码元速率为100pps。IRIG-B码有3种码元,二进制“0”、“1”和位置识别标志Px,脉宽分别为2ms、5ms和8ms。脉冲信号如图1.3所示。

图1.3IRIG-B码元图

连续2个“P”码元表示整秒的开始,第2个“P”码元的脉冲前沿是“准时”参考点,定义其为“Pr”,后面携带当前的时间和时间控制相关的信息。IRIG-B的整秒“准时”参考点,SMV的采样计数器的需要清零,这点和PPS是一样的,如图1.2所示。

如图1.4所示为DT6000E的IRIG-B对时。

图1.4IRIG-B对时

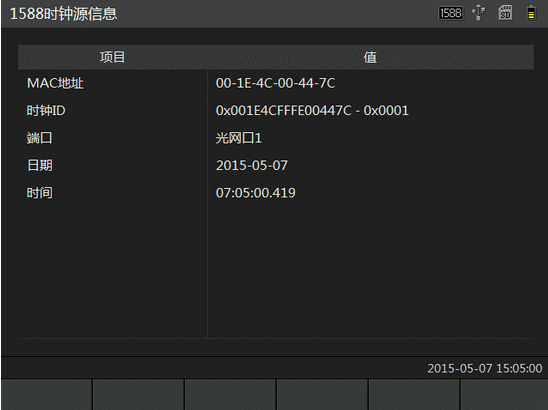

3.IEEE1588对时

IEEE1588报文的解码和打时标都是在FPGA中进行的,工作在Slave模式。打时标是指在同步报文进入或者离开协议栈的时候,用本地时钟信息标记同步报文的过程。时间戳的获取方式直接影响时钟同步的精度,获取时间戳的地点约接近物理层,越能很好的避开报文在协议栈中的延时抖动,所能够达到的同步精度也就越高。在FPGA中进行报文解码和打时标为在MII层打时标,为硬件打时标,精度最高。

如图1.5所示为DT6000E的IEEE1588对时。

图1.5IEEE1588对时

二、校时

DT6000系列在对时的同时会进行校时,校正本地晶振的误差值。图1.6为校时调整的一个实例说明图,由图中可以看出第一次粗略调节值为+99,第二次精确调节为正向,此时的Value=+99+9=+108,第三次精确调节为反向,此时的Value=+108-2=+106,在获取Value值的同时计数器也在一直均匀的调节。

图1.6校时实例说明图

校时电路(FPGA)工作在100MHz主频下,经过实际测量,校正稳定之后,温度变化不大的环境下,其精度误差不超过20个周期(10ns),经过校时之后,对时精度从μs级可变为200ns级。并且采用校时电路之后,在移除校时设备之后都能长时间保持本地的时间的高准确度。

三、授时

DT6000系列支持IRIG-B码和PPS的授时,DT6000S有两个光串口,因此支持两个光串口同时授时。如图1.7所示为DT6000E的IRIG-B码授时界面,PPS的授时等同。

图1.7IRIG-B码授时

责任编辑:电朵云